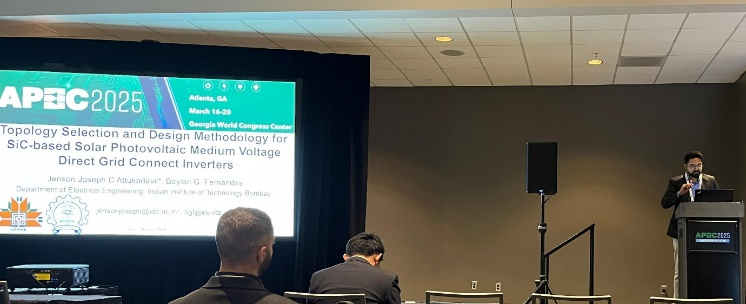

NCPRE participated in the 2025 IEEE Applied Power Electronics Conference (APEC), held in Atlanta, USA, from March 16–20, 2025. At the conference, NCPRE student Jenson Joseph C. A. presented the paper titled "Topology Selection and Design Methodology for SiC-Based Solar Photovoltaic Medium Voltage Direct Grid Connect Inverters," authored by J. J. C. Attukadavil and B. G. Fernandes. The paper introduces a comprehensive design methodology for several medium voltage inverter topologies, including three-level neutral point clamped (NPC) inverters, five-level active NPC inverters, three- and five-level modular multilevel converters, and cascaded H- bridge converter configurations. Key aspects covered in the methodology include SiC device selection, switching frequency optimization, filter design, and DC capacitor sizing. A refined, experimentally validated loss model based on 1700 V SiC MOSFETs was also introduced. The study offered a comparative analysis of factors like component count, efficiency, device stress, harmonic distortion, and total volume, helping identify the best fit for medium voltage PV applications. In addition to presenting the paper, the NCPRE team engaged with researchers across diverse fields, and attended several insightful technical sessions.

NCPRE’s Jenson Joseph presenting his paper at IEEE APEC 2025.